## смоз **МТ88Е39**

## Calling Number Identification Circuit Advance Information (CNIC1.1)

#### Features

- 1200 baud Bell 202 and CCITT V.23 Frequency Shift Keying (FSK) demodulation

- Compatible with Bellcore GR-30-CORE, SR-TSV-002476, TIA/EIA-716 and ETSI 300 778-1

- High input sensitivity

- Dual mode 3-wire data interface (Serial FSK data stream or MT88E43 compatible 1 byte buffer)

- Internal gain adjustable amplifier

- · Carrier detect status output

- Uses 3.579545 MHz crystal or ceramic resonator

- 3 to 5V ±10% supply voltage

- Low power CMOS with power down mode

- Direct pin to pin replacement of MT8841 and MT88E41

## **Applications**

- Global (North America, Japan, Europe) FSK based CID (Calling Identity Delivery) / CLIP (Calling Line Identity Presentation)

- Feature phones, adjunct boxes

- FAX machines

- Telephone answering machines

- Computer Telephony Integration (CTI)

- Battery powered applications

| S5035                 |  | November 1998 |  |  |  |  |  |  |  |  |

|-----------------------|--|---------------|--|--|--|--|--|--|--|--|

| Ordering Information  |  |               |  |  |  |  |  |  |  |  |

| MT88E39AS 16 Pin SOIC |  |               |  |  |  |  |  |  |  |  |

-40 to +85 °C

## Description

D

The MT88E39 Calling Number Identification Circuit (CNIC1.1) is a CMOS integrated circuit which provides an interface to calling line information delivery services that utilize 1200 baud Bell 202 or CCITT V.23 FSK data transmission schemes. The MT88E39 receives and demodulates the FSK signal and outputs the data into a simple dual mode 3-wire serial interface which eliminates the need for an UART.

The MT88E39 is Bellcore, ETSI and NTT compatible and can operate in 3V and 5V applications. It is a pin to pin replacement of the MT8841 and MT88E41 by operating in the MT88E41 FSK interface mode (mode 0) when placed in a MT88E41 socket. New designs may also choose the MT88E43 compatible interface (mode 1) where the microcontroller reads the FSK byte from a 1 byte buffer.

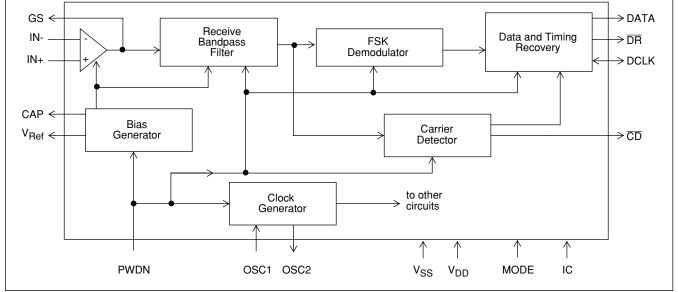

Figure 1 - Functional Block Diagram

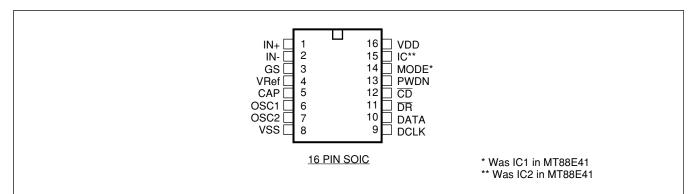

## Figure 2 - Pin Connections

## **Pin Description**

| Pin # | Name             | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|-------|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1     | IN+              | Non-inverting Op-Amp (Input).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 2     | IN-              | Inverting Op-Amp (Input).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 3     | GS               | Gain Select (Output). Gives access to op-amp output for connection of feedback resistor.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 4     | V <sub>Ref</sub> | Voltage Reference (Output). Nominally $V_{DD}/2$ . This is used to bias the op-amp inputs.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 5     | CAP              | <b>Capacitor.</b> Connect a $0.1\mu$ F capacitor to V <sub>SS</sub> .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 6     | OSC1             | <b>Oscillator (Input).</b> Crystal connection. This pin can be driven directly from an external clocking source.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 7     | OSC2             | <b>Oscillator (Output).</b> Crystal connection. When OSC1 is driven by an external clock, this pin should be left open.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 8     | $V_{SS}$         | Power supply ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 9     | DCLK             | <b>3-wire FSK Interface: Data Clock (CMOS Output/Schmitt Input).</b> In mode 0 (MT88E41 compatible mode - when the MODE pin is logic low) this is a CMOS output which denotes the nominal mid-point of a FSK data bit.<br>In mode 1 (when the MODE pin is logic high) this is a Schmitt trigger input used to shift the FSK data byte out to the DATA pin.                                                                                                                                                                                                                                                                                                                  |

| 10    | DATA             | <b>3-wire FSK Interface: Data (CMOS Output).</b> In mode 0 (MT88E41 compatible mode - when the MODE pin is logic low) the FSK serial bit stream is output to DATA as demodulated. Mark frequency corresponds to logical 1. Space frequency corresponds to logical 0. In mode 1 (when the MODE pin is logic high) the start and stop bits are stripped off and only the data byte is stored in a 1 byte buffer. At the end of each word signalled by the DR pin, the microcontroller should shift the byte out to DATA pin by applying 8 read pulses at the DCLK pin.                                                                                                        |

| 11    | DR               | <b>3-wire FSK Interface: Data Ready (Open Drain/CMOS Output).</b> Active low. In mode 0 (MT88E41 compatible mode - when the MODE pin is logic low) this is an open drain output. In mode 1 (when the MODE pin is logic high) this is a CMOS output. This pin denotes the end of a word. Typically, DR is used to interrupt the microcontroller. It is normally hi-Z or high (modes 0 and 1 respectively) and goes low for half a bit time at the end of a word. But in mode 1 if DCLK begins during DR low, the first rising edge of the DCLK input will return DR to high. This feature allows an interrupt requested by DR to be cleared upon reading the first DATA bit. |

| 12    | CD               | <b>Carrier Detect (Open Drain/CMOS Output).</b> Active low. In mode 0 (MT88E41 compatible mode - when the MODE pin is logic low) this is an open drain output. In mode 1 (when the MODE pin is logic high) this is a CMOS output.<br>A logic low indicates that a carrier has been present for a specified time on the line. A time hysteresis is provided to allow for momentary discontinuity of carrier. The demodulated FSK data is inhibited until the carrier has been detected.                                                                                                                                                                                      |

| 13    | PWDN             | <b>Power Down (Schmitt Input).</b> Active high. Powers down the device including the input op-amp and the oscillator. Must be low for operation.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Pin # | Name            | Description                                                                                                                                                                                                                                                                                                                                         |

|-------|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 14    | MODE            | <b>Mode select (Input).</b> This pin selects the 3-wire FSK interface mode. To select mode 0 (MT88E41 compatible mode) this pin should be logic low. To select mode 1 this pin should be logic high.<br>Because this pin is already connected to Vss in 'E41 applications, the MT88E39 can replace the 'E41 without any circuit or software change. |

| 15    | IC              | Internal Connection. Internal connection. Leave open circuit. In MT88E41, this was IC2 which was also left open in the application circuit.                                                                                                                                                                                                         |

| 16    | V <sub>DD</sub> | Positive power supply voltage.                                                                                                                                                                                                                                                                                                                      |

## Pin Description

## **Functional Description**

The MT88E39 is a FSK demodulator compatible with FSK based Caller ID services around the world, such as in North America, France, Germany, and Japan. Caller ID is the generic term for a group of services offered by telephone operating companies whereby information about the calling party is delivered to the subscriber. In the FSK based methods, the information is modulated in either Bell 202 (in North America) or CCITT V.23 (in Europe) FSK format and transmitted at 1200 baud from the serving end office to the subscriber's terminal.

In North America, Caller ID uses the voiceband data transmission interface defined in the Bellcore document GR-30-CORE. The terminal or CPE (Customer Premises Equipment) requirements are defined in Bellcore document SR-TSV-002476. Typical services are CND (Calling Number Delivery), CNAM (Calling Name Delivery), VMWI (Visual Message Waiting Indicator) and CIDCW (Calling Identity Delivery on Call Waiting).

In on-hook Caller ID, such as CND and CNAM, the information is typically transmitted from the end office before the subscriber picks up the phone. There are various methods such as between the first and second rings (North America), between an abbreviated ring and the first true ring (Japan, France and Germany). On-hook Caller ID can also occur without ringing for services such as VMWI. The MT88E39 is suitable for these forms of alerting.

In off-hook Caller ID, such as CIDCW, information about a new calling party is sent to the subscriber who is already engaged in a call. Bellcore's method uses a special dual tone known as CAS (CPE Alerting Signal) which should be detected by the CPE. After the CPE has acknowledged with a DTMF digit, the end office will send the FSK data. The MT88E39 is suitable for receiving the FSK data but a separate CAS detector is required. The MT88E39 provides an interface to the Caller ID physical layer. It bandpass filters and demodulates the 1200 baud FSK signal. It also provides a convenient interface to extract the demodulated FSK data. Although the main application of the MT88E39 is Caller ID, it can also be used wherever 1200 baud Bell 202 and/or CCITT V.23 FSK reception is required.

#### 3 to 5V operation

The MT88E39 can operate from 5.5V down to 2.7V, but the FSK reject level will change with Vdd. In a battery powered CPE, the FSK accept level will become lower as the batteries are run down. If the CPE is designed for 4.5V, the accept level will be lowered when the batteries drain to 3V. In North America there is a requirement for rejecting FSK signals which are below 3 mVrms when data is not preceded by ringing, such as VMWI (Visual Message Waiting Indicator) applications. When the batteries are drained, the CPE will not meet the reject level. For on-hook Caller ID, there is no reject level and the CPE will meet all requirements.

#### Input Configuration

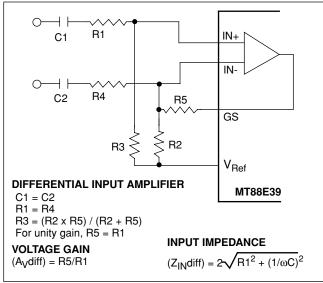

The input arrangement of the MT88E39 provides an operational amplifier, as well as a bias source ( $V_{Ref}$ ) which is used to bias the inputs at  $V_{DD}/2$ . Provision is made for connection of a feedback resistor to the op-amp output (GS) for adjustment of gain.

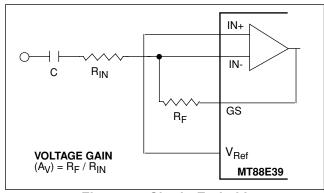

Figure 3 shows the necessary connections for a differential input configuration. In a single-ended configuration, the input pins are connected as shown in Figure 4.

Figure 3 - Differential Input Configuration

#### Figure 4 - Single-Ended Input Configuration

#### 3-wire FSK Data Interface

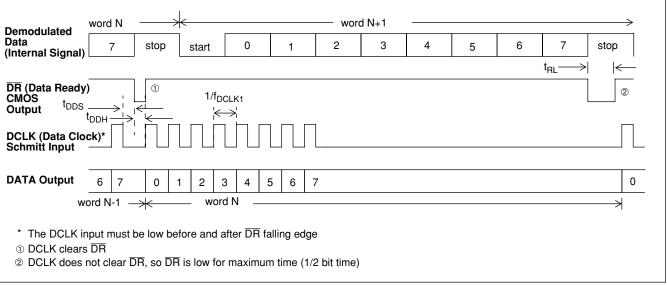

The MT88E39 provides a powerful dual mode 3-wire interface so that the 8-bit data words in the demodulated FSK bit stream can be extracted without the need either for an external UART or for the microcontroller to perform the UART function in software. The interface is specifically designed for the 1200 baud rate and is comprised of the DATA, DCLK (data clock) and  $\overline{DR}$  (data ready) pins. Two modes (0 and 1) are selectable via control of the device's MODE pin. In mode 0 the FSK bit stream is output as demodulated. In mode 1 the FSK data byte is store in a 1 byte buffer. Note that in mode 0  $\overline{DR}$  and  $\overline{CD}$  are open drain outputs; in mode 1 they are CMOS outputs. DCLK is an output in mode 0.

#### Mode 0

This mode is selected when the MODE pin is low. It is the MT88E41 compatible mode where the FSK data stream is output as demodulated. Since the MODE pin was IC1 in MT88E41 and connected to Vss, the MT88E39 will work in mode 0 when placed in a MT88E41 socket.

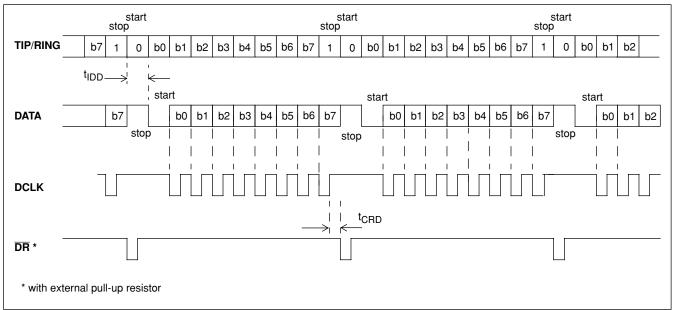

In this mode, the MT88E39 receives the FSK signal, demodulates it, and outputs the data directly to the DATA pin (see Figure 11). For each received stop and start bit sequence, the MT88E39 outputs a fixed frequency clock string of 8 pulses at the DCLK pin. Each DCLK rising edge occurs in the nominal centre of a data bit. DCLK is not generated for the stop and start bits. Consequently, DCLK will clock only valid data into a peripheral device such as a serial to parallel shift register or a microcontroller. The MT88E39 also outputs an end of word pulse (Data Ready) on the  $\overline{DR}$  pin, which indicates the reception of every 10-bit word (counting the start and stop bits) sent from the end office. DR can be used to interrupt a microcontroller or cause a serial to parallel converter to parallel load its data into a microcontroller. The mode 0 DATA pin can also be connected to a personal computer's serial communication port after converting from CMOS to RS-232 voltage levels.

#### Mode 1

This mode is selected when the MODE pin is high. In this mode, the microcontroller supplies read pulses at the DCLK pin (which is now an input) to shift the 8-bit data words out of the MT88E39, onto the DATA pin. The MT88E39 asserts  $\overline{DR}$  to denote the word boundary and indicate to the microprocessor that a new word has become available (see Figure 12).

Internal to the MT88E39, the demodulated data bits are sampled and stored. The start and stop bits are stripped off. After the 8th bit, the data byte is parallel loaded into an 8 bit shift register and  $\overline{DR}$  goes low. The shift register's contents are shifted out to the DATA pin on the supplied DCLK's rising edge in the order they were received.

If DCLK begins while  $\overline{DR}$  is low,  $\overline{DR}$  will return to high upon the first DCLK. This feature allows the associated interrupt to be cleared by the first read pulse. Otherwise  $\overline{DR}$  is low for half a nominal bit time (1/2400 sec). After the last bit has been read, additional DCLKs are ignored.

Note that in both modes, the 3-pin interface may also output data generated by speech or other voiceband

signals. The user may choose to ignore these outputs when FSK data is not expected, or force the MT88E39 into its power down mode.

#### **Power Down Mode**

For applications requiring reduced power consumption, the MT88E39 can be forced into power down when it is not needed. This is done by pulling the PWDN pin high. In power down mode, the oscillator, op-amp and internal circuitry are all disabled and the MT88E39 will not react to the input signal.  $\overline{DR}$  and  $\overline{CD}$  are at high impedance or at logic high (modes 0 and 1 respectively). In mode 0, DATA and DCLK are at logic high. The MT88E39 can be awakened for reception of the FSK signal by pulling the PWDN pin low.

#### **Carrier Detect**

The carrier detector provides an indication of the presence of a signal in the FSK frequency band. It detects the presence of a signal of sufficient amplitude at the output of the FSK bandpass filter. The signal is qualified by a digital algorithm before the CD output is set low to indicate carrier detection. A 10ms hysteresis is provided to allow for momentary signal drop out once CD has been activated. CD is released when there is no activity at the FSK bandpass filter output for 10 ms.

When  $\overline{CD}$  is inactive (high), the raw output of the demodulator is ignored by the data timing recovery circuit (see Figure 1). In mode 0, the DATA pin is forced high. No DCLK or  $\overline{DR}$  signal is generated. In mode 1, the internal shift register is not updated and no  $\overline{DR}$  is generated. If DCLK is clocked (in mode 1), DATA is undefined.

Note that signals such as CAS, speech and DTMF tones also lie in the FSK frequency band and the carrier detector may be activated by these signals. They will be demodulated and presented as data. To avoid false data, the PWDN pin should be used to disable the FSK demodulator when no FSK signal is expected.

Ringing, on the other hand, does not pose a problem as it is ignored by the carrier detector.

#### **Crystal Oscillator**

The MT88E39 uses either a 3.579545MHz ceramic resonator or crystal oscillator as the master timing source.

The crystal specification is as follows:

| Frequency:                 | 3.579545 MHz      |

|----------------------------|-------------------|

| Frequency tolerance:       | ±0.2%(-40°C+85°C) |

| Resonance mode:            | Parallel          |

| Load capacitance:          | 18 pF             |

| Maximum series resistance: | 150 ohms          |

| Maximum drive level (mW):  | 2 mW              |

| e.g. CTS MP036S            |                   |

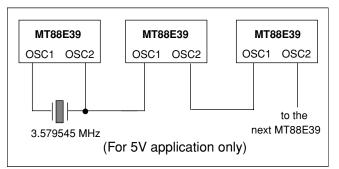

Figure 5 - Common Crystal Connection

For 5V applications any number of MT88E39 devices can be connected as shown in Figure 5 such that only one crystal is required. The connection between OSC2 and OSC1 can be DC coupled as shown, or the OSC1 input on all devices can be driven from a CMOS buffer (dc coupled) with the OSC2 outputs left unconnected.

#### V<sub>Ref</sub> and CAP Inputs

$V_{Ref}$  is the output of a low impedance voltage source equal to  $V_{DD}/2$  and is used to bias the input op-amp. A 0.1µF capacitor is required between CAP and  $V_{SS}$ to suppress noise on  $V_{Ref}$ .

## **Applications**

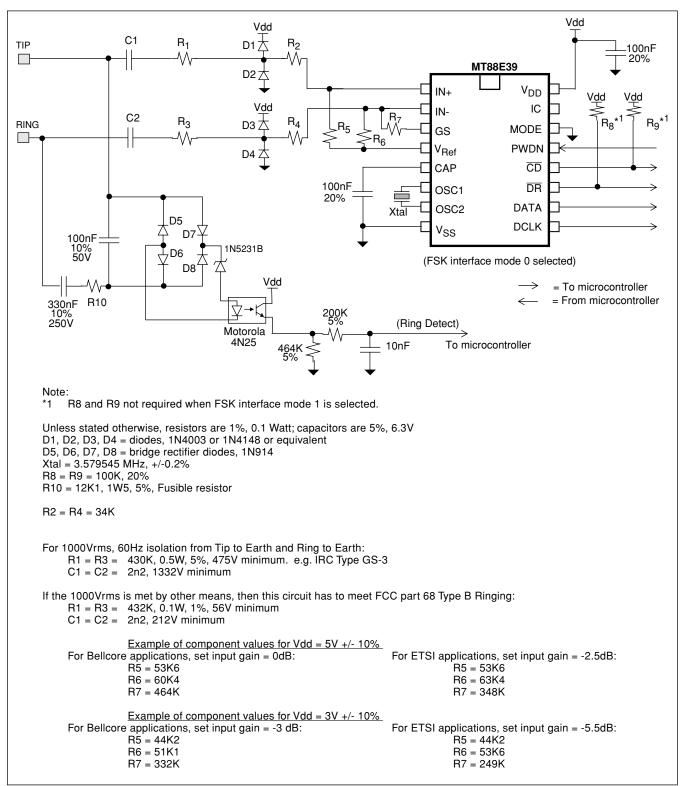

Table 1 shows the Bellcore and ETSI FSK signal characteristics. The application circuit in Figure 6 will meet these requirements.

For 5V designs the input op-amp should be set to unity gain to meet the Bellcore requirements and -2.5 dB gain for ETSI requirements.

As supply voltage  $(V_{DD})$  is decreased, the FSK detect threshold will be lowered. Therefore for designs operating at other than 5V nominal voltage, to meet the FSK reject level requirement the gain of the op-amp should be reduced accordingly.

For 3V designs the gain settings for Bellcore and ETSI should be -3dB and -5.5dB respectively.

For applications requiring detection of lower FSK signal level, the input op-amp may be configured to provide adequate gain. However, too much gain will cause noise tolerance to fail the TIA requirements because the FSK signal will be clipped at GS when the single tone noise is added.

| Parameter                                   | North America: Bellcore *1                                                                                                                                                          | Europe: ETSI <sup>*2</sup>                                          |

|---------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------|

| Mark (logical 1) frequency                  | 1200 Hz +/- 1%                                                                                                                                                                      | 1300 Hz +/- 1.5%                                                    |

| Space (logical 0) frequency                 | 2200 Hz +/- 1%                                                                                                                                                                      | 2100 Hz +/- 1.5%                                                    |

| Received signal level                       | -36.20 to -4.23 dBm <sup>*3</sup><br>(12 to 476 mVrms)                                                                                                                              | -33.78 to -5.78 dBm<br>(-36 to -8 dBV <sup>*4</sup> ) <sup>*5</sup> |

| Reject signal level                         | -48.23 dBm (3 mVrms)<br>(VMWI only)                                                                                                                                                 | -47.78 dBm (-50 dBV)                                                |

| Transmission rate                           | 1200 baud +/- 1%                                                                                                                                                                    | 1200 baud +/- 1%                                                    |

| Twist                                       | -6 to +10 dB                                                                                                                                                                        | -6 to +6 dB                                                         |

| Signal to noise ratio                       | Single tone (f):<br>-18 dB (f<=60Hz)<br>-12 dB (60 <f<=120hz)<br>-6 dB (120<f<=200hz)<br>+25 dB (200<f<3200hz)<br>+6 dB (f&gt;=3200Hz)</f<3200hz)<br></f<=200hz)<br></f<=120hz)<br> | >= 25 db<br>(300 to 3400 Hz)                                        |

| MT88E39 FSK input gain<br>for Vdd=5V +/-10% | 0 dB                                                                                                                                                                                | -2.5 dB                                                             |

#### Table 1 - FSK signal characteristics specified by some standard bodies

Notes:

\*1: Recommended by TIA/EIA-716. Bellcore has agreed to the values and will incorporate them into its future standards.

\*2: ETS 300 778-1 (On-hook) Sep 97, ETS 300 778-2 (Off-hook) Jan 97.

\*3: dBm = Decibels above or below a reference power of 1mW into 600 ohms. 0dBm=0.7746Vrms.

\*4: dBV = Decibels above or below a reference voltage of 1Vrms. dBV=1Vrms.

\*5: On-hook signal range. The Off-hook signal levels are inside this range: -30.78 to -7.78 dBm.

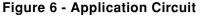

Figure 7 - Application Circuit (multiple interrupt source)

|   | Parameter                                                       | Symbol           | Min    | Max                  | Units |

|---|-----------------------------------------------------------------|------------------|--------|----------------------|-------|

|   | i didineter                                                     | Cymbol           | IVIIII | Max                  | Onits |

| 1 | DC Power Supply Voltage $V_{DD}$ to $V_{SS}$                    | V <sub>DD</sub>  | -0.3   | 6                    | V     |

| 2 | Voltage on any pin                                              | V <sub>P</sub>   | -0.3   | V <sub>DD</sub> +0.3 | V     |

| 3 | Current at any pin (except $V_{\text{DD}}$ and $V_{\text{SS}})$ | I <sub>I/O</sub> |        | ±10                  | mA    |

| 4 | Storage Temperature                                             | T <sub>ST</sub>  | -65    | +150                 | °C    |

| 5 | Package Power Dissipation                                       | P <sub>D</sub>   |        | 500                  | mW    |

#### Absolute Maximum Ratings\* - Voltages are with respect to V<sub>SS</sub> unless otherwise stated.

\* Exceeding these values may cause permanent damage. Functional operation under these conditions is not implied.

#### Recommended Operating Conditions - Voltages are with respect to ground (VSS) unless otherwise stated

|   | Characteristics              | Sym              | Min | Тур      | Max  | Units | Test Conditions |

|---|------------------------------|------------------|-----|----------|------|-------|-----------------|

| 1 | DC Power Supply Voltage      | V <sub>DD</sub>  | 2.7 |          | 5.5  | V     |                 |

| 2 | Clock Frequency              | f <sub>OSC</sub> |     | 3.579545 |      | MHz   |                 |

| 3 | Tolerance on Clock Frequency | ∆fc              |     |          | ±0.2 | %     |                 |

| 4 | Operating Temperature        |                  | -40 |          | +85  | °C    |                 |

## DC Electrical Characteristics<sup>†</sup>

|    |                        | Characteristics                                                                        | Sym                                | Min                                          | Тур*       | Мах                                          | Units    | Test<br>Conditions                                      |

|----|------------------------|----------------------------------------------------------------------------------------|------------------------------------|----------------------------------------------|------------|----------------------------------------------|----------|---------------------------------------------------------|

| 1  | S                      | Standby Supply Current                                                                 | I <sub>DDQ</sub>                   |                                              | 0.1        | 15                                           | μA       | Notes* 1                                                |

| 2  | U<br>P<br>L<br>Y       | Operating Supply Current<br>V <sub>DD</sub> =3.0V, 25°C<br>V <sub>DD</sub> =5.0V, 25°C | I <sub>DD</sub>                    |                                              | 1.2<br>1.9 | 2.0<br>3.0                                   | mA<br>mA | Notes* 2                                                |

| 3  | DR,<br>CD,             | Sink Current                                                                           | I <sub>OL</sub>                    | 2.5                                          |            |                                              | mA       | $V_{OL}$ =0.1 $V_{DD}$                                  |

| 4  | DATA,<br>DCLK          | Source current<br>DATA<br>DCLK (in mode 0)<br>DR, CD (in mode 1)                       | I <sub>OH</sub>                    | 0.8                                          |            |                                              | mA       | V <sub>OH</sub> =0.9V <sub>DD</sub>                     |

| 5  | DR, CD                 | Output hi-Z current<br>(in mode 0)                                                     | I <sub>OZ</sub>                    |                                              |            | 10                                           | μA       | $V_{\text{OZ}}\text{=}V_{\text{SS}}$ to $V_{\text{DD}}$ |

| 6  | PWDN,<br>DCLK<br>(in   | Schmitt Input High Threshold<br>Schmitt Input Low Threshold                            | V <sub>T+</sub><br>V <sub>T-</sub> | 0.48*V <sub>DD</sub><br>0.28*V <sub>DD</sub> |            | 0.68*V <sub>DD</sub><br>0.48*V <sub>DD</sub> | V<br>V   |                                                         |

| 7  | mode 1)                | Schmitt Hysteresis                                                                     | $V_{HYS}$                          | 0.2                                          |            |                                              | V        |                                                         |

| 8  | MODE                   | CMOS Input High Voltage<br>CMOS Input Low Voltage                                      | V <sub>IH</sub><br>V <sub>IL</sub> | 0.7*V <sub>DD</sub><br>V <sub>SS</sub>       |            | V <sub>DD</sub><br>0.3*V <sub>DD</sub>       | V        |                                                         |

| 9  | PWDN,<br>DCLK,<br>MODE | Input Current                                                                          | I <sub>IN</sub>                    |                                              |            | 10                                           | μA       | $V_{SS} \le V_{IN} \le V_{DD}$                          |

| 10 | VRef                   | Output Voltage                                                                         | V <sub>Ref</sub>                   | 0.5*V <sub>DD</sub> - 0.1                    |            | 0.5*V <sub>DD</sub> + 0.1                    | V        | No Load                                                 |

| 11 |                        | Output Resistance                                                                      | R <sub>Ref</sub>                   |                                              |            | 2                                            | kΩ       |                                                         |

† DC Electrical Characteristics are over recommended operating conditions unless otherwise stated.

\* Typical figures are at 25°C and are for design aid only.

Notes\*: 1.PWDN=Vdd. FSK input = 0 mVrms. Digital inputs at either Vdd or Vss. No current drawn from output pins.

2.PWDN=Vss. FSK input = 0 mVrms. With no current drawn from Vref, OSC2 and all digital pins.

|    | Characteristics              | Sym              | Min | Тур‡ | Max                  | Units | Test Conditions                      |

|----|------------------------------|------------------|-----|------|----------------------|-------|--------------------------------------|

| 1  | Input Leakage Current        | I <sub>IN</sub>  |     |      | 1                    | μA    | $V_{SS} \le V_{IN} \le V_{DD}$       |

| 2  | Input Resistance             | R <sub>in</sub>  | 5   |      |                      | MΩ    |                                      |

| 3  | Input Offset Voltage         | V <sub>OS</sub>  |     |      | 25                   | mV    |                                      |

| 4  | Power Supply Rejection Ratio | PSRR             | 30  |      |                      | dB    | 1kHz ripple on V <sub>DD</sub>       |

| 5  | Common Mode Rejection        | CMRR             | 30  |      |                      | dB    | $V_{CMmin} \le V_{IN} \le V_{CMmax}$ |

| 6  | DC Open Loop Voltage Gain    | A <sub>VOL</sub> | 40  |      |                      | dB    |                                      |

| 7  | Unity Gain Bandwidth         | f <sub>C</sub>   | 0.2 |      |                      | MHz   |                                      |

| 8  | Output Voltage Swing         | Vo               | 0.5 |      | V <sub>DD</sub> -0.7 | V     | Load $\geq$ 100k $\Omega$            |

| 9  | Capacitive Load (GS)         | CL               |     |      | 50                   | pF    |                                      |

| 10 | Resistive Load (GS)          | RL               | 100 |      |                      | kΩ    |                                      |

| 11 | Common Mode Voltage Range    | V <sub>CM</sub>  | 1.0 |      | V <sub>DD</sub> -1.0 | V     |                                      |

## Electrical Characteristics<sup>†</sup> - Gain Setting Amplifier

† Electrical characteristics are over recommended operating conditions, unless otherwise stated.

<sup>‡</sup> Typical figures are at 25°C and are for design aid only: not guaranteed and not subject to production testing.

## AC Electrical Characteristics<sup>†</sup> - FSK

|   | Characteristics                                                                                                     | Sym | Min                              | Typ <sup>‡</sup>             | Max                              | Units                | Notes*                                                                   |

|---|---------------------------------------------------------------------------------------------------------------------|-----|----------------------------------|------------------------------|----------------------------------|----------------------|--------------------------------------------------------------------------|

| 1 | Input Detection Level                                                                                               |     | -37.78<br>-40<br>10              |                              | -1.78<br>-4<br>631               | dBm<br>dBV<br>mVrms  | 1, 2, 3, 4                                                               |

| 2 | Input Baud Rate                                                                                                     |     | 1188                             | 1200                         | 1212                             | baud                 | 6                                                                        |

| 3 | Input Frequency Detection<br>Bell 202 1 (Mark)<br>Bell 202 0 (Space)<br>CCITT V.23 1 (Mark)<br>CCITT V.23 0 (Space) |     | 1188<br>2178<br>1280.5<br>2068.5 | 1200<br>2200<br>1300<br>2100 | 1212<br>2222<br>1319.5<br>2131.5 | Hz<br>Hz<br>Hz<br>Hz | <ul> <li>BELL 202 Frequencies</li> <li>CCITT V.23 Frequencies</li> </ul> |

| 4 | Input Noise Tolerance 20 log (signal noise)                                                                         | SNR | 20                               |                              |                                  | dB                   | 3, 4, 5                                                                  |

| 5 | Twist=20 log $(\frac{V_{Mark}}{V_{Space}})$                                                                         |     | -6                               |                              | 10                               | dB                   |                                                                          |

† AC Electrical Characteristics are over recommended operating conditions, unless otherwise stated.

<sup>‡</sup> Typical figures are at 25°C and are for design aid only: not guaranteed and not subject to production testing.

Notes\*:

1. dBm = Decibels above or below a reference power of 1mW into  $600\Omega$ . 0dBm=0.7746Vrms.

dBV = Decibels above or below a reference voltage of 1Vrms. 0dBV=1Vrms.

Input op-amp configured to 0dB gain at Vdd=5V+/-10%, -3dB at Vdd=3V+/-10%.

4. Mark and Space frequencies have the same amplitude. 5. Band limited random noise (200-3400Hz). Present when FSK signal present. 6. OSC1 at 3.579545 MHz  $\pm$ 0.2%.

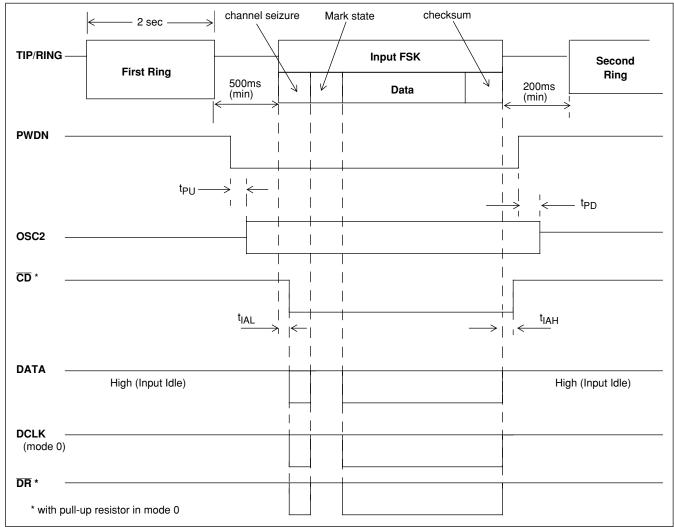

|   |      | Characteristics                                | Sym              | Min | Typ‡ | Max  | Units | Notes* |

|---|------|------------------------------------------------|------------------|-----|------|------|-------|--------|

| 1 | PWDN | Power-up time                                  | t <sub>PU</sub>  |     |      | 50   | ms    |        |

| 2 | OSC1 | Power-down time                                | t <sub>PD</sub>  |     | 100  | 1000 | μs    | 1      |

| 3 |      | Input FSK to $\overline{\text{CD}}$ low delay  | t <sub>IAL</sub> |     |      | 25   | ms    |        |

| 4 | CD   | Input FSK to $\overline{\text{CD}}$ high delay | t <sub>IAH</sub> | 10  |      |      | ms    |        |

| 5 |      | Hysteresis                                     |                  | 10  |      |      | ms    |        |

#### AC Electrical Characteristics<sup>†</sup> - Timing

† AC Electrical Characteristics are over recommended operating conditions unless otherwise stated.

‡ Typical figures are at 25°C and are for design aid only, not guaranteed and not subject to production testing.

Notes\*: 1. The device will stop functioning within this time, but more time may be required to reach IDDQ.

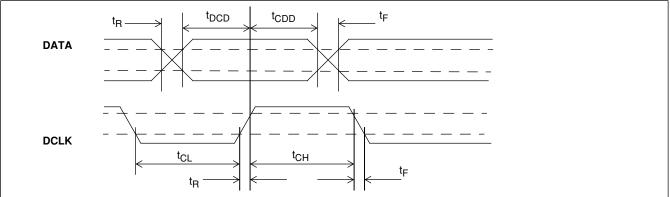

## AC Electrical Characteristics<sup>†</sup> - 3-Wire FSK Interface Timing (Mode 0)

|    |                | Characteristics               | Sym              | Min    | Typ <sup>‡</sup> | Max    | Units | Notes*     |

|----|----------------|-------------------------------|------------------|--------|------------------|--------|-------|------------|

| 1  | DATA           | Rate                          |                  | 1188   | 1200             | 1212   | bps   | 1, 6       |

| 2  |                | Input FSK to DATA delay       | t <sub>IDD</sub> |        | 1                | 5      | ms    |            |

| 3  |                | Rise time                     | t <sub>R</sub>   |        |                  | 200    | ns    | 3          |

| 4  | DATA           | Fall time                     | t <sub>F</sub>   |        |                  | 200    | ns    | 3          |

| 5  | DCLK           | DATA to DCLK delay            | t <sub>DCD</sub> | 6      | 416              |        | μs    | 1, 2, 5, 6 |

| 6  |                | DCLK to DATA delay            | t <sub>CDD</sub> | 6      | 416              |        | μs    | 1, 2, 5, 6 |

| 7  |                | Frequency                     |                  | 1200.4 | 1202.8           | 1205.2 | Hz    | 2          |

| 8  | DCLK           | High time                     | t <sub>CH</sub>  | 415    | 416              | 417    | μs    | 2          |

| 9  |                | Low time                      | t <sub>CL</sub>  | 415    | 416              | 417    | μs    | 2          |

| 10 | DCLK<br>DR     | DCLK to $\overline{DR}$ delay | t <sub>CRD</sub> | 415    | 416              | 417    | μs    | 2          |

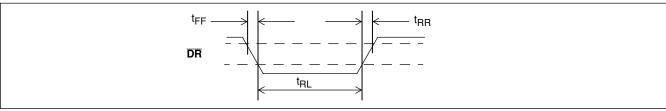

| 11 |                | Rise time                     | t <sub>RR</sub>  |        |                  | 10     | μs    | 4          |

| 12 | DR             | Fall time                     | t <sub>FF</sub>  |        |                  | 200    | ns    | 4          |

| 13 | la atula at Ok | Low time                      | t <sub>RL</sub>  | 415    | 416              | 417    | μs    | 2          |

† AC Electrical Characteristics are over recommended operating conditions unless otherwise stated.

<sup>‡</sup> Typical figures are at 25°C and are for design aid only, not guaranteed and not subject to production testing.

Notes\*:

1. FSK input data at 1200  $\pm$ 12 baud. 2. OSC1 at 3.579545 MHz  $\pm$ 0.2%. 3. 10k to V<sub>SS</sub>, 50pF to V<sub>SS</sub>. 4. 10k to V<sub>DD</sub>, 50pF to V<sub>SS</sub>. 5. Function of signal condition. 6. For a repeating mark space seque

6. For a repeating mark space sequence, the data stream will typically have equal 1 and 0 bit durations.

## AC Electrical Characteristics<sup>†</sup> - 3-Wire FSK Interface Timing (Mode 1)

|   |      | Characteristics                               | Sym                | Min | Typ <sup>‡</sup> | Мах | Units | Notes*      |

|---|------|-----------------------------------------------|--------------------|-----|------------------|-----|-------|-------------|

| 1 |      | Frequency                                     | f <sub>DCLK1</sub> |     |                  | 1   | MHz   | See Fig. 12 |

| 2 | DCLK | Duty Cycle                                    |                    | 30  |                  | 70  | %     |             |

| 3 |      | Rise Time                                     |                    |     |                  | 100 | ns    |             |

| 4 | DCLK | DCLK low setup time to $\overline{\text{DR}}$ | t <sub>DDS</sub>   | 500 |                  |     | ns    | See Fig. 12 |

| 5 | DR   | DCLK low hold time to $\overline{\text{DR}}$  | t <sub>DDH</sub>   | 500 |                  |     | ns    | See Fig. 12 |

† AC Electrical Characteristics are over recommended operating conditions unless otherwise stated.

<sup>‡</sup> Typical figures are at 25°C and are for design aid only, not guaranteed and not subject to production testing.

Figure 8 - DATA and DCLK Output Timing (Mode 0)

Figure 9 - DR Output Timing (Mode 0)

Figure 10 - Input and Output Timing (Bellcore CND Service)

## MT88E39 Advance Information

Figure 11 - Serial Data Interface Timing (Mode 0)

Figure 12 - Serial Data Interface Timing (Mode 1)

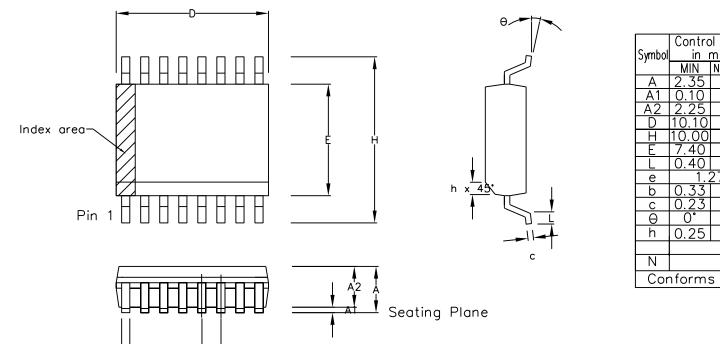

|                                   | Contro       | Dime     | nsions |  | Altern. Dimensi |         |       |  |

|-----------------------------------|--------------|----------|--------|--|-----------------|---------|-------|--|

| Symbol                            | in r         | nillimet | res    |  | i               | s       |       |  |

| ,                                 | MIN          | Nominal  | MAX    |  | MIN             | Nominal | MAX   |  |

| Α                                 | 2.35         |          | 2.65   |  | 0.093           |         | 0.104 |  |

| A1                                | 0.10         |          | 0.30   |  | 0.004           |         | 0.012 |  |

| A2                                | 2.25         |          | 2.35   |  | 0.089           |         | 0.092 |  |

| D                                 | 10.10        |          | 10.50  |  | 0.398           |         | 0.413 |  |

| Н                                 | 10.00        |          | 10.65  |  | 0.394           |         | 0.419 |  |

| E                                 | 7.40         |          | 7.60   |  | 0.291           |         | 0.299 |  |

| L                                 | 0.40         |          | 1.27   |  | 0.016           |         | 0.050 |  |

| е                                 | 1.27 BSC.    |          |        |  | 0.050 BSC.      |         |       |  |

| b                                 | 0.33         |          | 0.51   |  | 0.013           |         | 0.020 |  |

| С                                 | 0.23         |          | 0.32   |  | 0.009           |         | 0.013 |  |

| θ                                 | 0.           |          | 8      |  | 0°              |         | 8°    |  |

| h                                 | 0.25         |          | 0.75   |  | 0.010           |         | 0.029 |  |

|                                   | Pin features |          |        |  |                 |         |       |  |

| Ν                                 | 16           |          |        |  |                 |         |       |  |

| Conforms to JEDEC MS-013AA Iss. C |              |          |        |  |                 |         |       |  |

#### Notes:

- 1. The chamfer on the body is optional. If it not present, a visual index feature, e.g. a dot, must be located within the cross-hatched area.

- 2. Controlling dimension are in millimeters.

- J. Dimension D do not include mould flash, protrusion or gate burrs. These shall not exceed 0.006" per side.

J. Dimension E1 do not include inter-lead flash or protrusion. These shall not exceed 0.010" per side.

- 5. Dimension b does not include dambar protrusion/intrusion. Allowable dambar protrusion shall be 0.004" total in excess of b dimension.

| © Zarlink Semiconductor 2002 All rights reserved. |        |         |         | <br>          |                        | Package Code                        |  |  |

|---------------------------------------------------|--------|---------|---------|---------------|------------------------|-------------------------------------|--|--|

| ISSUE                                             | 1      | 2       | 3       |               | Previous package codes | Package Outline for                 |  |  |

| ACN                                               | 6745   | 201939  | 213097  | SEMICONDUCTOR | MP/S                   | 16 lead SOIC<br>(0.300" Body Width) |  |  |

| DATE                                              | 7Apr95 | 27Feb97 | 15Jul02 | JEMICONDOCTOR |                        |                                     |  |  |

| APPRD.                                            |        |         |         |               |                        | GPD00013                            |  |  |

# For more information about all Zarlink products visit our Web Site at

#### www.zarlink.com

Information relating to products and services furnished herein by Zarlink Semiconductor Inc. or its subsidiaries (collectively "Zarlink") is believed to be reliable. However, Zarlink assumes no liability for errors that may appear in this publication, or for liability otherwise arising from the application or use of any such information, product or service or for any infringement of patents or other intellectual property rights owned by third parties which may result from such application or use. Neither the supply of such information or purchase of product or service conveys any license, either express or implied, under patents or other intellectual property rights owned by Zarlink or licensed from third parties by Zarlink, whatsoever. Purchasers of products are also hereby notified that the use of product in certain ways or in combination with Zarlink, or non-Zarlink furnished goods or services may infringe patents or other intellectual property rights owned by Zarlink.

This publication is issued to provide information only and (unless agreed by Zarlink in writing) may not be used, applied or reproduced for any purpose nor form part of any order or contract nor to be regarded as a representation relating to the products or services concerned. The products, their specifications, services and other information appearing in this publication are subject to change by Zarlink without notice. No warranty or guarantee express or implied is made regarding the capability, performance or suitability of any product or service. Information concerning possible methods of use is provided as a guide only and does not constitute any guarantee that such methods of use will be satisfactory in a specific piece of equipment. It is the user's responsibility to fully determine the performance and suitability of any equipment using such information and to ensure that any publication or data used is up to date and has not been superseded. Manufacturing does not necessarily include testing of all functions or parameters. These products are not suitable for use in any medical products whose failure to perform may result in significant injury or death to the user. All products and materials are sold and services provided subject to Zarlink's conditions of sale which are available on request.

Purchase of Zarlink's I<sup>2</sup>C components conveys a licence under the Philips I<sup>2</sup>C Patent rights to use these components in and I<sup>2</sup>C System, provided that the system conforms to the I<sup>2</sup>C Standard Specification as defined by Philips.

Zarlink, ZL and the Zarlink Semiconductor logo are trademarks of Zarlink Semiconductor Inc.

Copyright Zarlink Semiconductor Inc. All Rights Reserved.

TECHNICAL DOCUMENTATION - NOT FOR RESALE